PKU crowned with laurels at ISSCC 2025

Mar 04, 2025

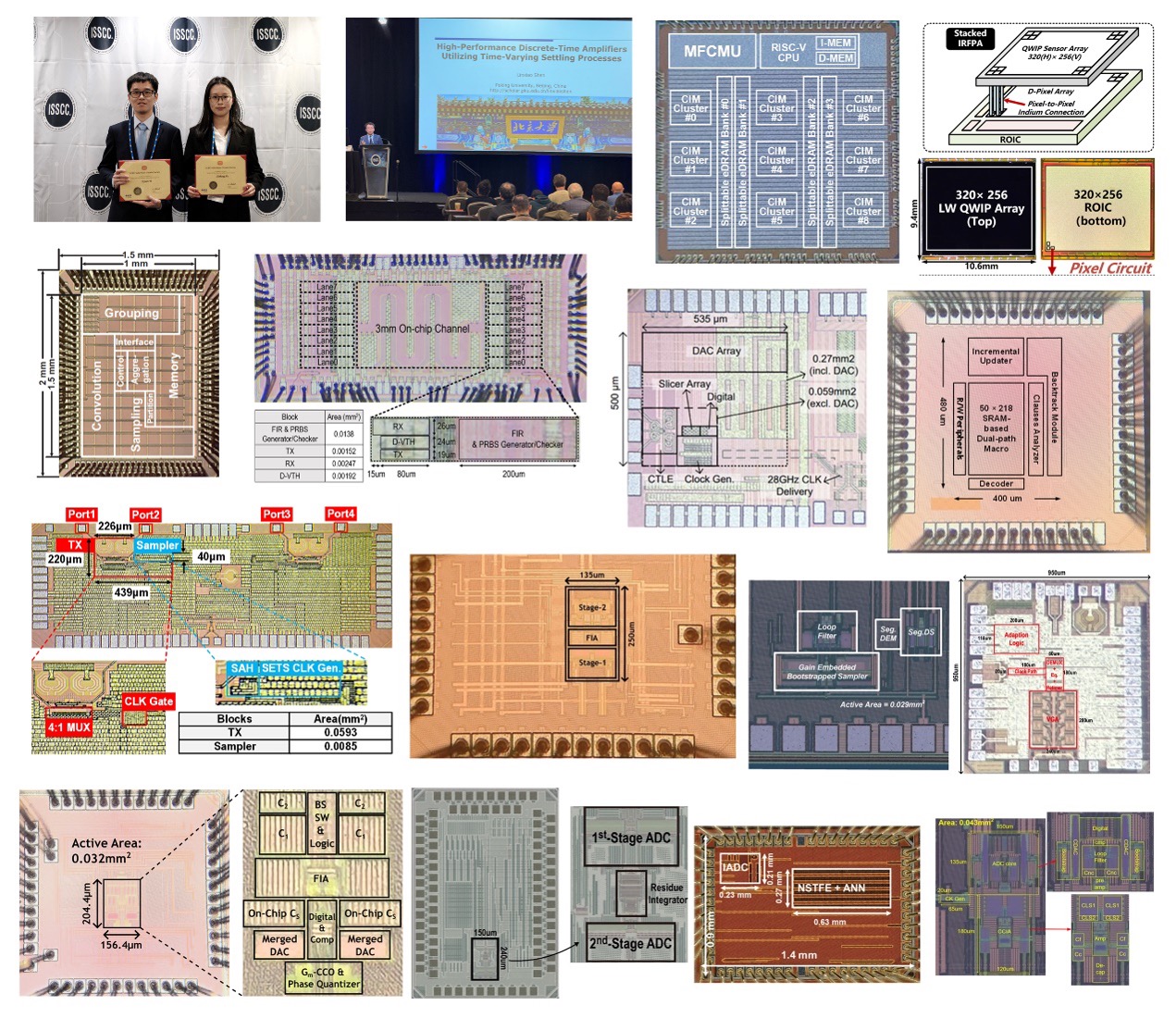

Peking University, March 4, 2025: 2025 International Solid-State Circuits Conference (ISSCC), recognized as the “Chip Olympics”, was held on February 16 to 20, 2025 in San Francisco, California. With 15 papers accepted, PKU School of Integrated Circuit, and Beijing Advanced Innovation Center for Integrated Circuits, made their presence felt through remarkable achievements in analog and mixed-signal, artificial intelligence and digital acceleration, imaging, wired communication, and other fields. Peking University was honored with the crown of laurels for having the most first-authored papers accepted, which include:

Four papers on AI and digital acceleration:

“SKADI: A 28nm Complete K-SAT Solver Featuring Dual-path SRAM-based Macro and Incremental Update with 100% Solvability”, first-authored by Wu Zihan

“A 22nm 60.81TFLOPS/W Diffusion Accelerator with Bandwidth-Aware Memory Partition and BL-Segmented Compute-in-Memory for Efficient Multi-Task Content Generation”, first-authored by Jing Yiqi

“A 0.22mm2161nW Noise-Robust Voice-Activity Detection Using Information-Aware Data Compression and Neuromorphic Spatial-Temporal Feature Extraction”, first-authored by Liu Ying, Li Jie, Zhang Qining

“A 28nm 109.8TOPS/W 3D PNN Accelerator Featuring Adaptive Partition, Multi-Skipping, and Block-Wise Aggregation”, first-authored by Zhou Changchun

One paper on image chip:

“A 320×256 6.9mW 2.2mK-NETD 120.4dB-DR LW-IRFPA with Pixel-Paralleled Light-Driven 20b Current-to-Phase ADC”, first-authored by Zhuo Yi

Four papers on wired communication:

“A 50Gb/s Burst-Mode NRZ Receiver with 5-Tap FFE, 7-Tap DFE and 15ns Lock Time in 28nm CMOS for Symmetric 50G-PON”, first-authored by Zhang Boyang, Ye Tianchen

“A 99.5mW/port DC-to-40GHz Integrated Channel Analyzer for High-Density Signal Integrity Measurement in 28nm CMOS”, first-authored by Wu Guangdong, Li Yuanliang, Ye Bingyi

“A 1.11pJ/b 224Gb/s XSR Receiver with Slice-Based CTLE and PI-Based Clock Generator in 12nm CMOS”, first-authored by Ye Bingyi

“A 64Gb/s/wire 10.5Tb/s/mm/layer Single-Ended Simultaneous Bi-Directional Transceiver with Echo and Crosstalk Cancellation for a Die-to-Die Interface in 28nm CMOS”, first-authored by Wang Zhifei

Six papers on analog and mixed-signal integrated circuit:

“A 12.2uW 99.6dB-SNDR 184.8dB-FOMs DT Zoom PPD ΔΣM with Gain-Embedded Bootstrapped Sampler”, first-authored by Luan Yaohui

“A 93.3dB SNDR, 180.4dB FoMs Calibration-Free Noise-Shaping Pipelined-SAR ADC with Cross-Stage Gain-Mismatch Error Shaping Technique and Negative-R-Assisted Residue Integrator”, first-authored by Gao Jihang

“A 184.8dB-FoMs 1.6MS/s Incremental Noise-Shaping Pipeline ADC with Single-Amplification-Based kT/C Noise Cancellation Technique”, first-authored by Wang Zongnan

“A Rail-to-Rail 3rd-Order Noise-Shaping SAR ADC Achieving 105.4dB SFDR with Integrated Input Buffer Using Continuous-Time Correlated Level Shifting”, first-authored by Ye Siyuan

“An Easy-Drive 16MS/s Pipelined-SAR ADC Using Split Coarse-Fine Input Buffer Sampling Scheme and Fast-Robust Background Inter-Stage Gain Calibration”, first-authored by Chen Zhuoyi

“A 185.2dB-FoMs 8.7-aFrms Zoomed Capacitance-to-Digital Converter with Chopping-Based kT/C Noise Cancellation and Add-Then-Subtract Phase-Domain Lead-Compensation Techniques”, first-authored by Li Bingrui

Research results

Written by: He Yike

Edited by: Zhang Jiang

Source: PKU News (Chinese)